Recent News

- 01/21/2026Our paper "A 40nm Programmable Heterogeneous SoC with RRAM/SRAM for Accelerating Neuro-Symbolic AI Models" accepted to JSSC.

- 11/07/2025Our paper "REASON: Accelerating Probabilistic Logical Reasoning for Neuro-Symbolic Cognitive Intelligence" accepted to HPCA 2026.

- 06/25/2025Our paper "Compositional AI Beyond LLMs: System Implications of Neuro-Symbolic-Probabilistic Architecture" accepted to ASPLOS 2026. [PDF]

- 04/15/2025Our tutorial paper "Efficient Processing of Neuro-Symbolic AI: A Tutorial and Cross-Layer Co-Design Case Study" accepted to NeuS 2025. [PDF]

- 03/03/2025Our paper "Generative AI in Embodied Systems: System-Level Analysis of Performance, Efficiency and Scalability" accepted to ISPASS 2025. [PDF]

- 02/15/2025Our paper "NSFlow: An End-to-End FPGA Framework with Scalable Dataflow Architecture for Neuro-Symbolic AI" accepted to DAC 2025. [PDF]

- 01/29/2025Our paper "ReCA: Integrated Acceleration for Real-Time and Efficient Cooperative Embodied Autonomous Agents" accepted to ASPLOS 2025. [PDF]

- 11/02/2024Our paper "CogSys: Efficient and Scalable Neurosymbolic Cognition System via Algorithm-Hardware Co-Design" accepted to HPCA 2025. [PDF]

- 08/04/2024Our invited paper "Towards Efficient Neuro-Symbolic AI: From Workload Characterization to Hardware Architecture" accepted to TCASAI. [PDF]

- 07/01/2024Our special session "Neuro-Symbolic Architecture Meets Large Language Models: A Memory-Centric Perspective" accepted to ESWEEK 2024. [PDF]

- 02/29/2024Our paper "Towards Cognitive AI Systems: Workload and Characterization of Neuro-Symbolic AI" accepted to ISPASS 2024. [PDF]

- 11/07/2023Our paper "H3DFACT: Heterogeneous 3D Integrated CIM for Factorization with Holographic Perceptual Representations" accepted to DATE 2024. [PDF]

- 04/10/2023Our paper "Towards Cognitive AI Systems: A Survey and Prospective on Neuro-Symbolic AI" accepted to SNAP workshop at MLSys 2023. [PDF]

Recent Talks

- 10/20/2025 "Tailored Computing: Cross-Layer System, Architecture, and Silicon Co-Design for Physical Intelligence" at MICRO PhD Forum, Seoul, Korea.

- 09/05/2025 "System Implications and Opportunities for Compositional Neuro-Symbolic-Probabilistic AI" at Georgia Tech (Host: Dr. Alexey Tumanov), Atlanta, GA.

- 07/11/2025 "Demystifying Neuro-Symbolic AI for Software-Hardware Co-Design" at Purdue University (Host: Dr. Anand Raghunathan), West Lafayette, IN.

- 07/10/2025 "Demystifying Neuro-Symbolic AI for Software-Hardware Co-Design" at University of Notre Dame (Host: Dr. Ningyuan Cao), South Bend, IN.

- 06/24/2025 "Tailored Computing: Domain-Specific Hardware and Systems for Embodied Cognitive Intelligence" at DAC PhD Forum, San Francisco, CA. [Slide]

- 06/24/2025 "NSFlow: An End-to-End FPGA Framework with Scalable Dataflow Architecture for Neuro-Symbolic AI" at DAC, San Francisco, CA. [Slide]

- 06/21/2025 "Efficient and Safe Embodied Intelligence: From Benchmarking to Co-Design" at ISCA Arch4EAI Workshop, Tokyo, Japan. [Slide]

- 05/30/2025 "Efficient Processing of Neuro-Symbolic AI: A Tutorial and Co-Design Case Study" at NeuS, University of Pennsylvania, Philadelphia, PA.

- 05/11/2025 "Generative AI in Embodied Systems: System-Level Analysis of Performance, Efficiency and Scalability" at ISPASS, Ghent, Belgium. [Slide]

- 04/17/2025 "Demystifying Neuro-Symbolic AI for Software-Hardware Co-Design" at Google (Host: Dr. Suvinay Subramanian), Mountain View, CA. [Slide]

- 04/02/2025 "ReCA: Integrated Acceleration for Real-Time and Efficient Cooperative Embodied Autonomous Agents" at ASPLOS, Rotterdam, the Netherlands. [Slide]

- 03/31/2025 "Demystifying Neuro-Symbolic AI for Software-Hardware Co-Design" at ASPLOS MLBench Workshop, Rotterdam, the Netherlands. [Slide]

- 03/22/2025 "Bridging Learning and Reasoning: A Cross-Layer Software-Architecture-FPGA-SoC Approach for Neuro-Symbolic AI" at DARPA JUMP2.0 CoCoSys Annual Review, Atlanta, GA.

- 03/13/2025 "Programmable Silicon Prototyping for Various Neuro-Symbolic Models" at CoCoSys Industry Meeting, Atlanta, GA.

- 03/04/2025 "CogSys: Efficient and Scalable Neurosymbolic Cognition System via Algorithm-Hardware Co-Design AI" at HPCA, Las Vegas, NV. [Slide]

- 03/01/2025 "Towards Cognitive AI Systems: Workload and Characterization of Neuro-Symbolic AI" at HPCA MLBench Workshop, Las Vegas, NV. [Slide]

- 02/25/2025 "Tailored Computing: Domain-Specific Architecture for Embodied Cognitive Intelligence" at UIUC, Urbana-Champaign, IL. [Slide]

- 02/13/2025 "CogSys: Efficient and Scalable Neurosymbolic Cognition System via Algorithm-Hardware Co-Design AI" at CRNCH Summit, Atlanta, GA.

- 02/03/2025 "Tailored Computing: Domain-Specific Architecture for Embodied Cognitive Intelligence" at University of Washington (Host: Dr. Ang Li), Seattle, WA. [Slide]

- 01/28/2025 "Towards Cognitive AI Systems: Workload and Characterization of Neuro-Symbolic AI", at Georgia Tech (Host: Dr. Callie Hao), Atlanta, GA. [Slide]

- 01/24/2025 "Demystifying Neuro-Symbolic AI for Software-Hardware Co-Design" at Georgia Tech Computer Architecture Research Seminar, Atlanta, GA.

- 11/15/2024 "System-Architecture-Technology Cross-Layer Design for Embodied Intelligence" at Harvard University (Host: Dr. Gage Hills), Cambridge, MA.

- 11/07/2024 "Tailored Computing: Domain-Specific Architecture for Cognitive Intelligence" at University of Central Florida (Host: Dr. Di Wu), Orlando, FL. [Slide]

- 11/05/2024 "Efficient and Scalable Neurosymbolic System via Algorithm-Hardware Co-Design" at ACM Student Research Competition, MICRO, Austin, TX. [Slide]

- 11/03/2024 "Intelligence in Embodied Systems: Cross-Layer Co-Design for Intelligent Autonomous Machines" at MICRO RoboArch Workshop, Austin, TX. [Slide]

- 10/01/2024 "Neuro-Symbolic Architecture Meets Large Language Models: A Memory-Centric Perspective" at ESWEEK, Raleigh, NC. [Slide]

- 09/09/2024 "H3DFACT: Heterogeneous 3D Integrated CIM for Factorization with Holographic Perceptual Representations" at SRC TECHCON, Austin, TX. [Slide]

- 08/15/2024 "Towards Cognitive AI Systems: Workload and Characterization of Neuro-Symbolic AI" at University of Minnesota, Minneapolis, MN. [Slide]

- 05/07/2024 "Towards Cognitive AI Systems: Workload and Characterization of Neuro-Symbolic AI" at ISPASS, Indianapolis, IN. [Slide]

- 04/27/2024 "Towards Cognitive AI Systems: Workload and Characterization of Neuro-Symbolic AI" at ASPLOS EMC2 Workshop, San Diego, CA. [Slide]

- 03/22/2024 "H3DFACT: Heterogeneous 3D Integrated CIM for Factorization with Holographic Perceptual Representations" at DATE, Valencia, Spain. [Slide]

Abstract

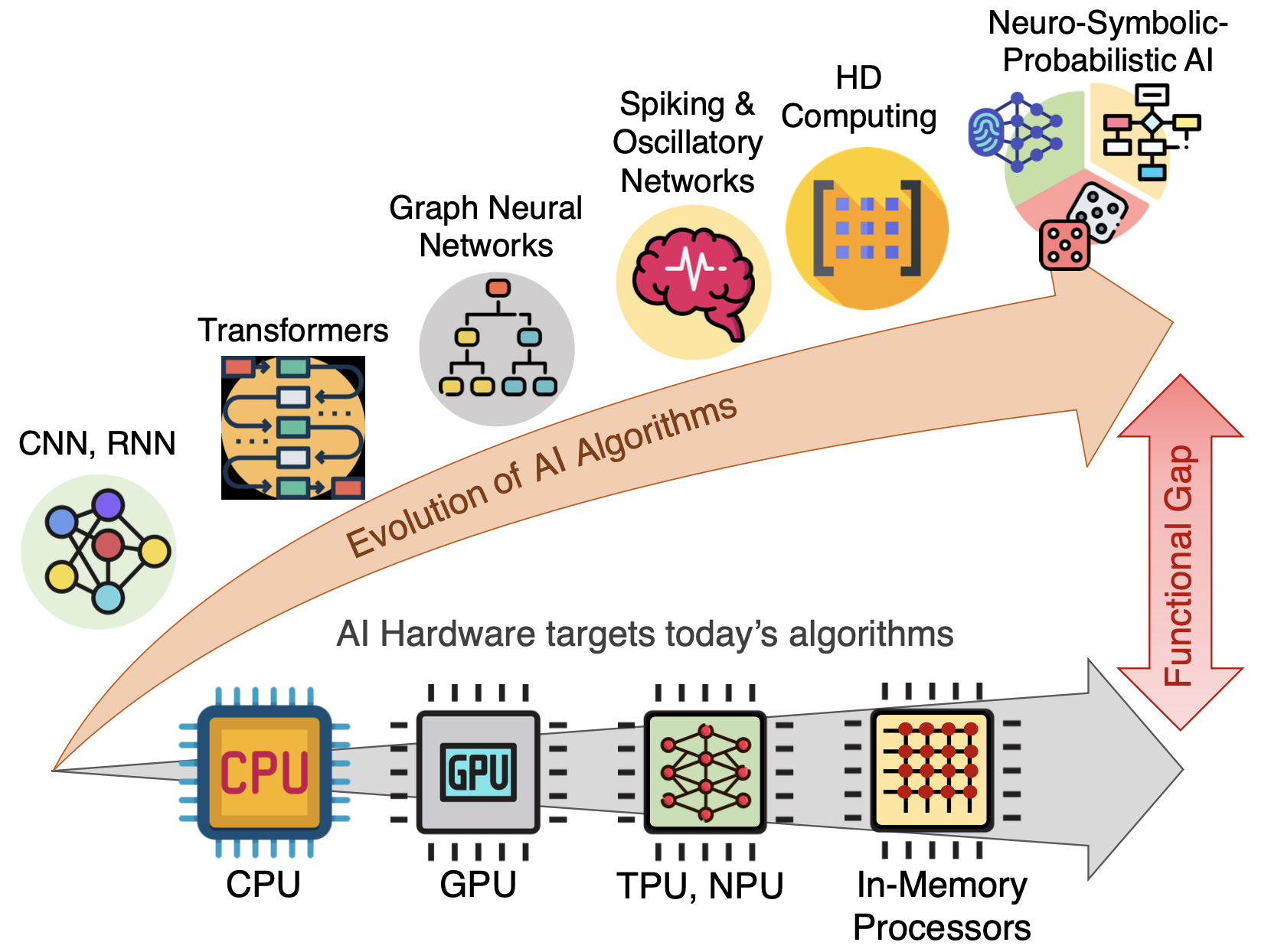

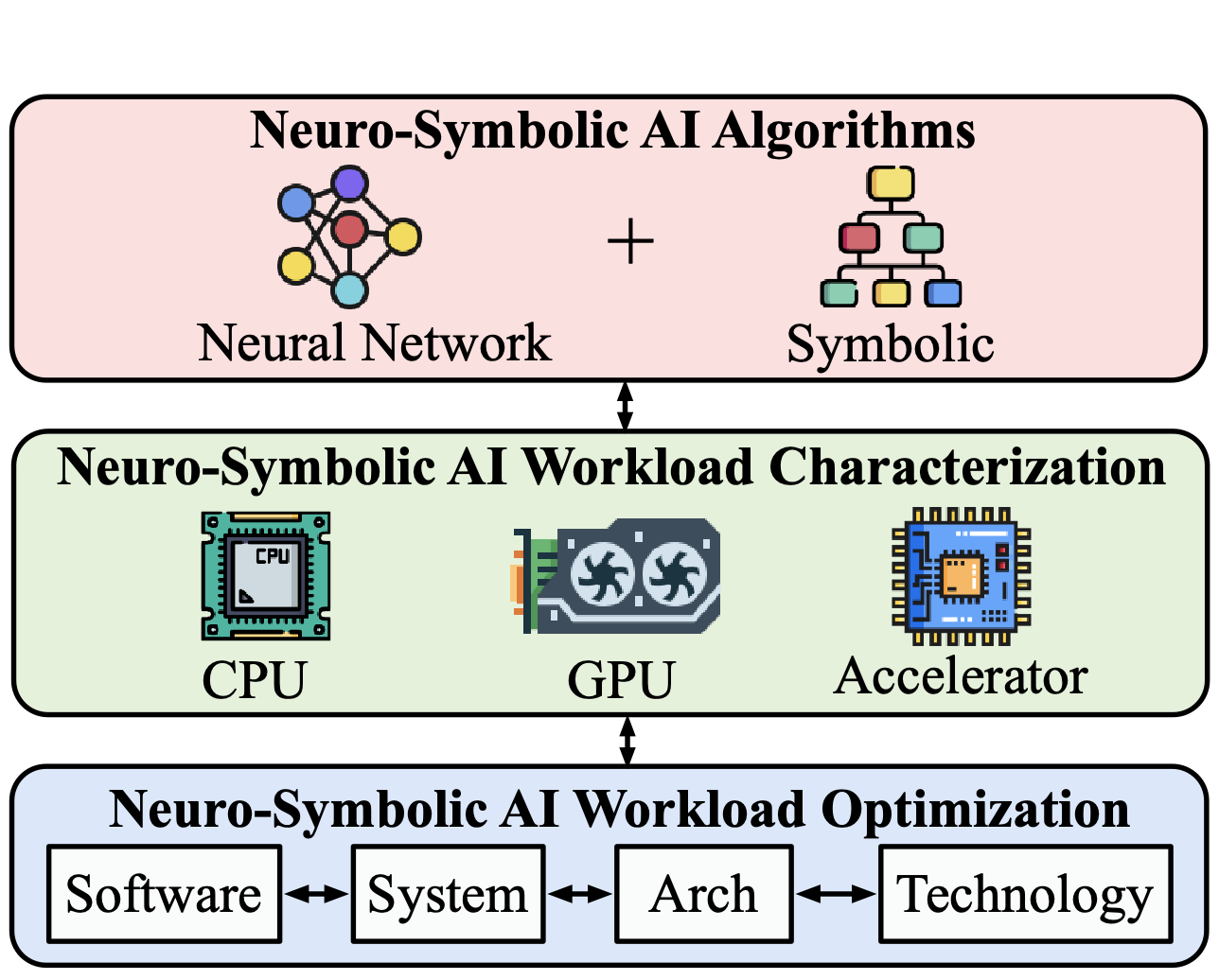

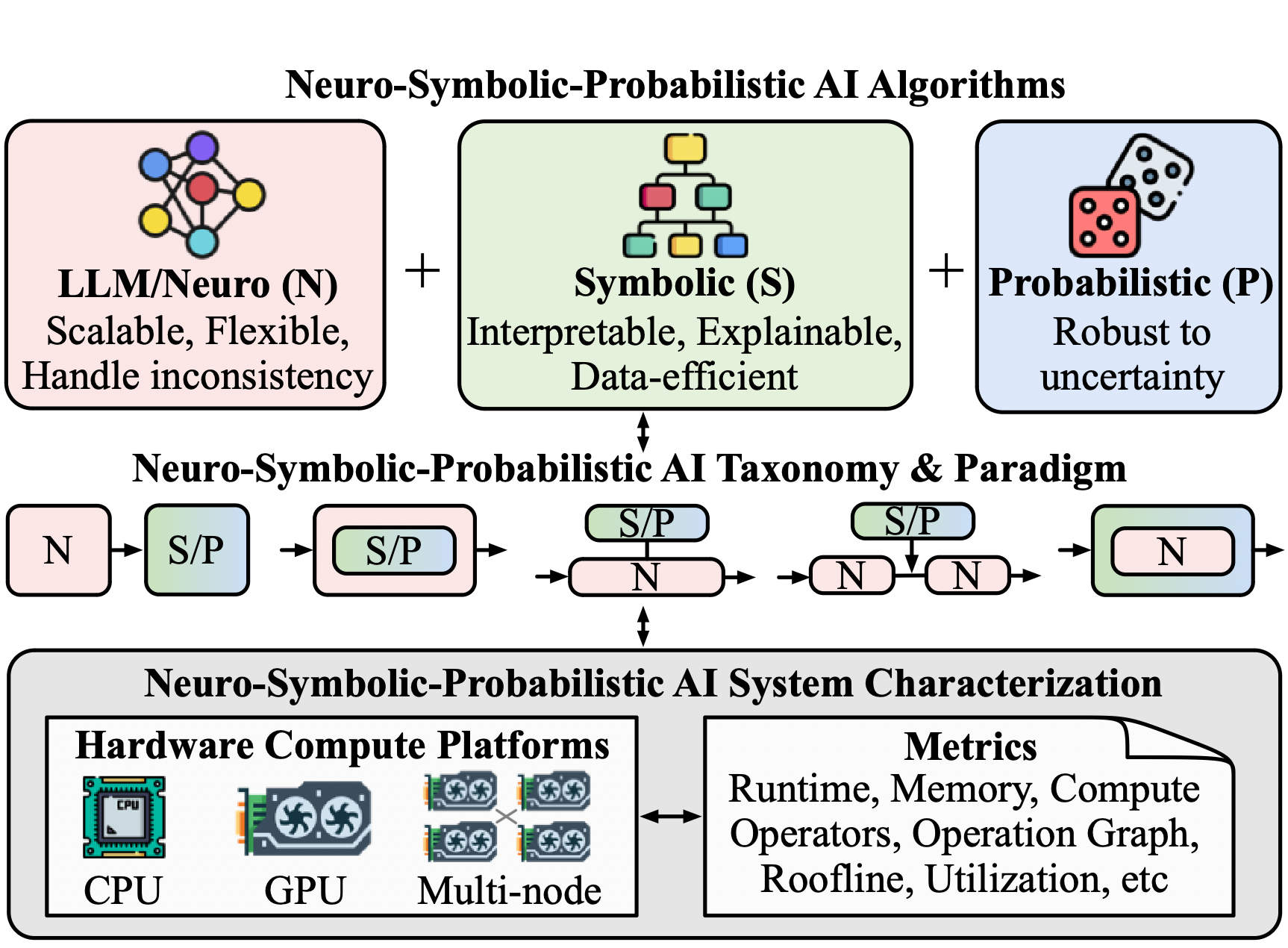

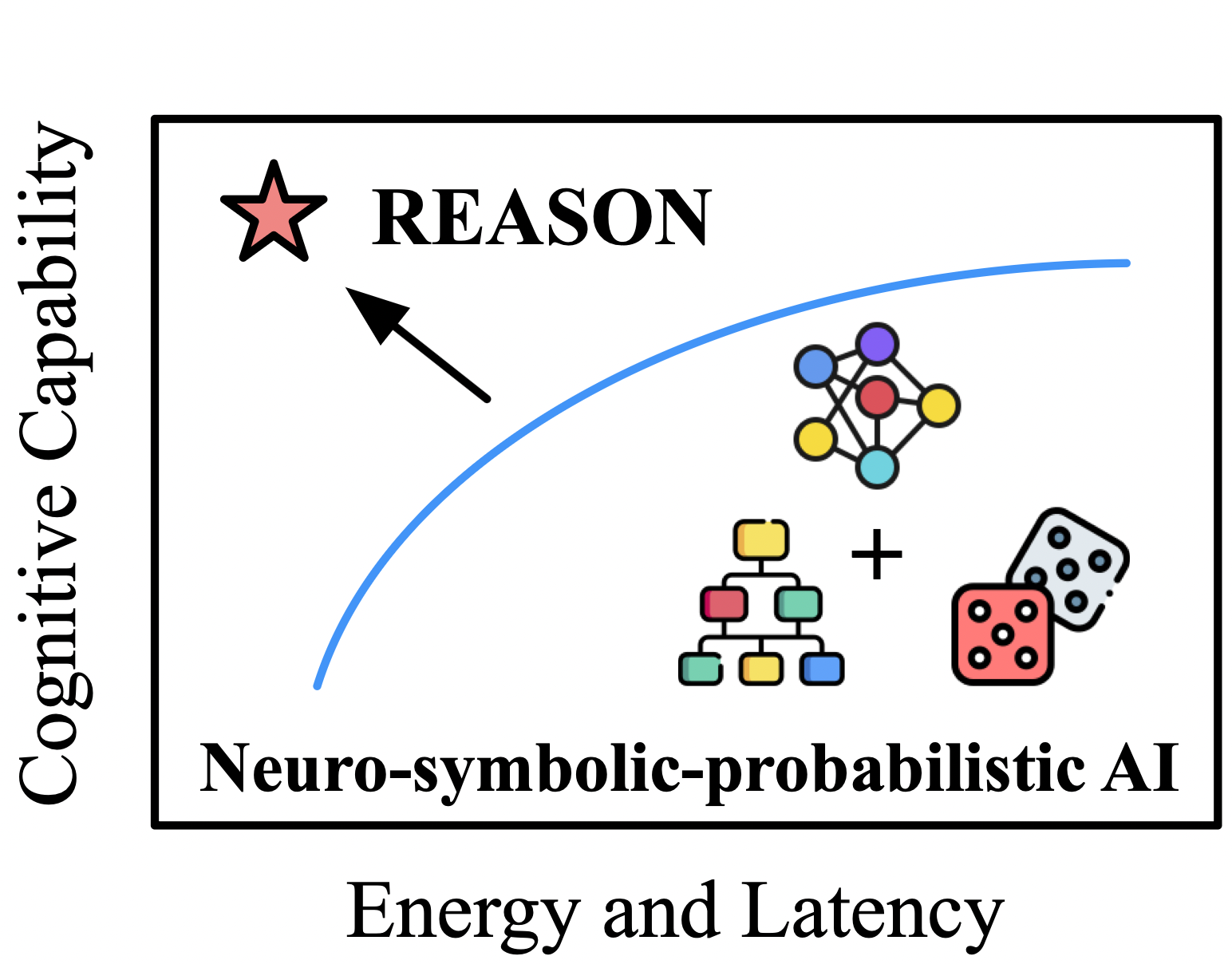

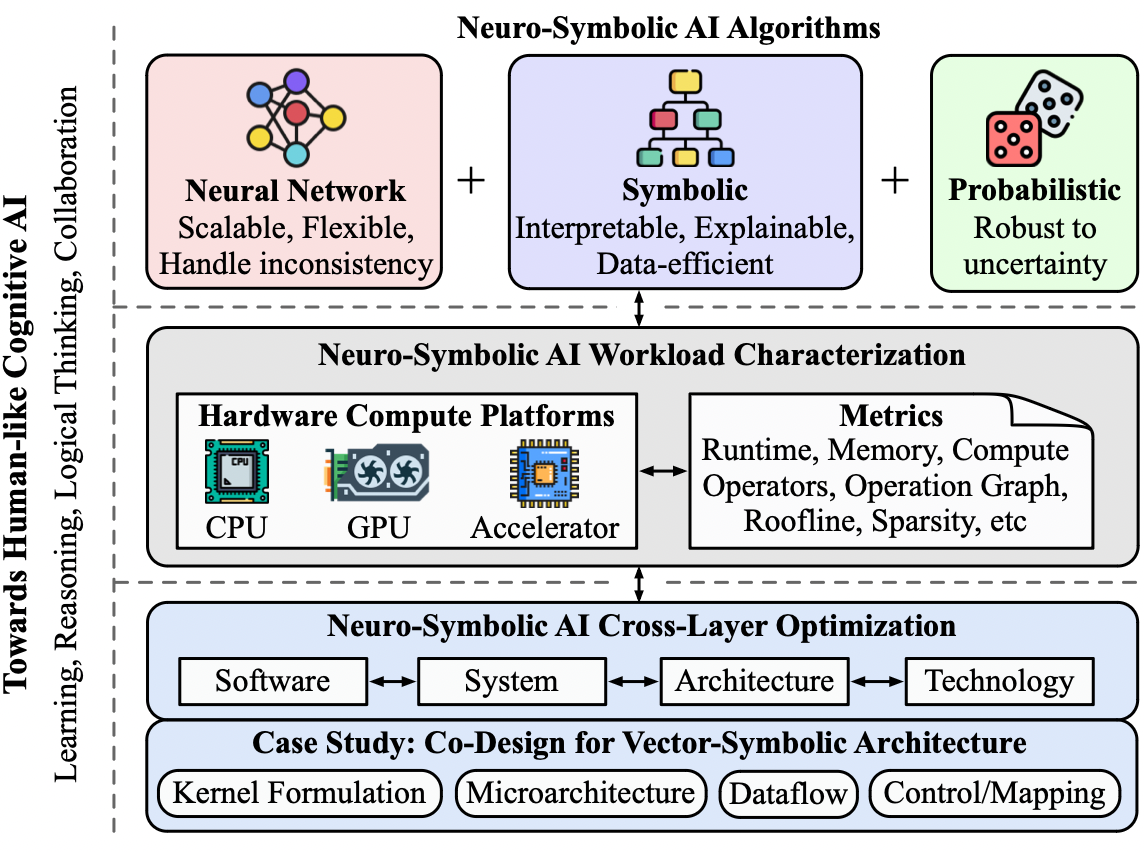

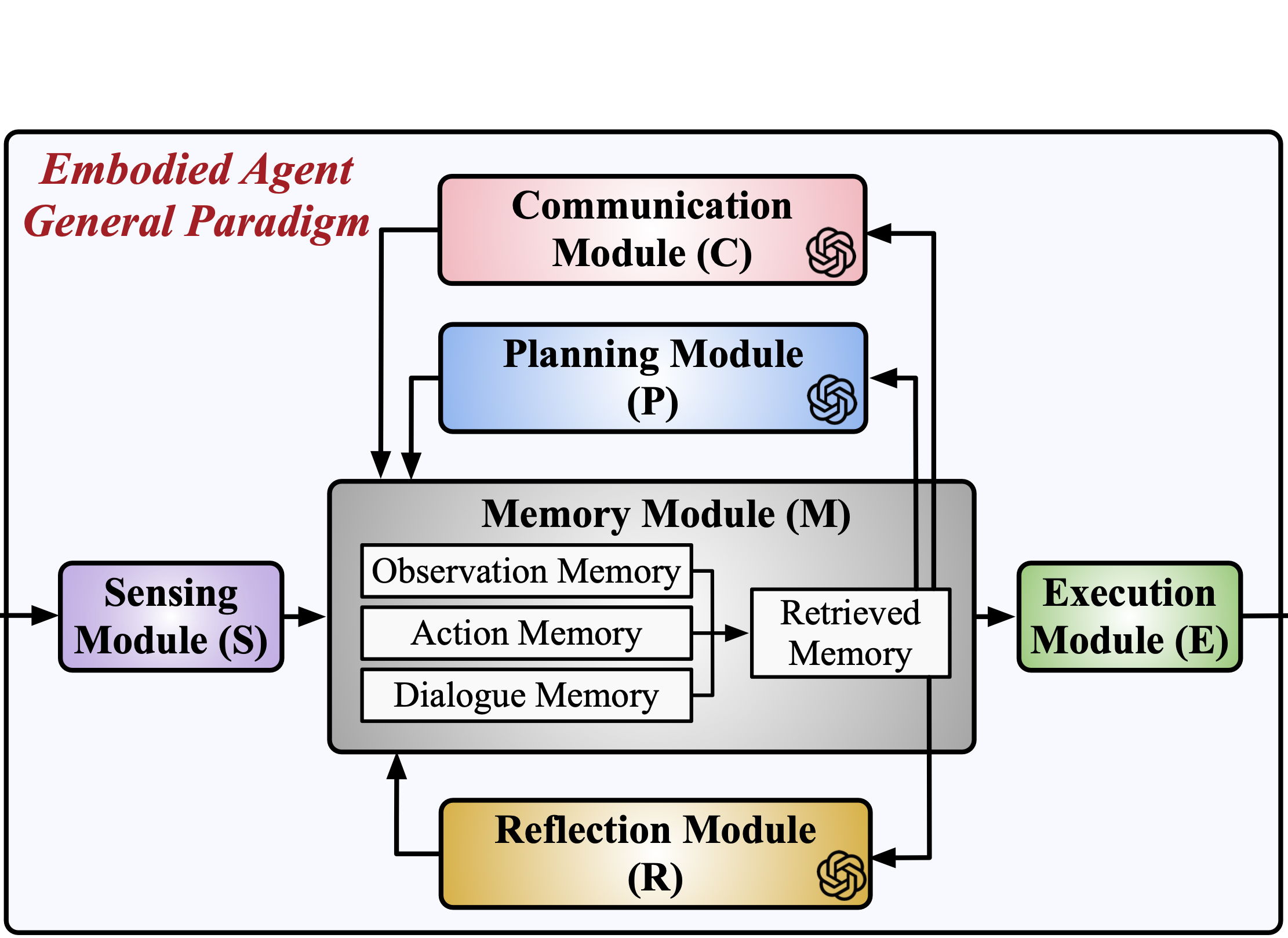

Neuro-symbolic AI presents an emerging compositional paradigm that fuses neural learning with symbolic reasoning and probabilistic inference to enhance the transparency, interpretability, and trustworthiness of AI solutions for complex real-world tasks. However, achieving real-time, energy-efficient, and scalable deployment of neuro-symbolic intelligence requires cross-disciplinary integration through application discovery, systems thinking, and co-design intelligence.

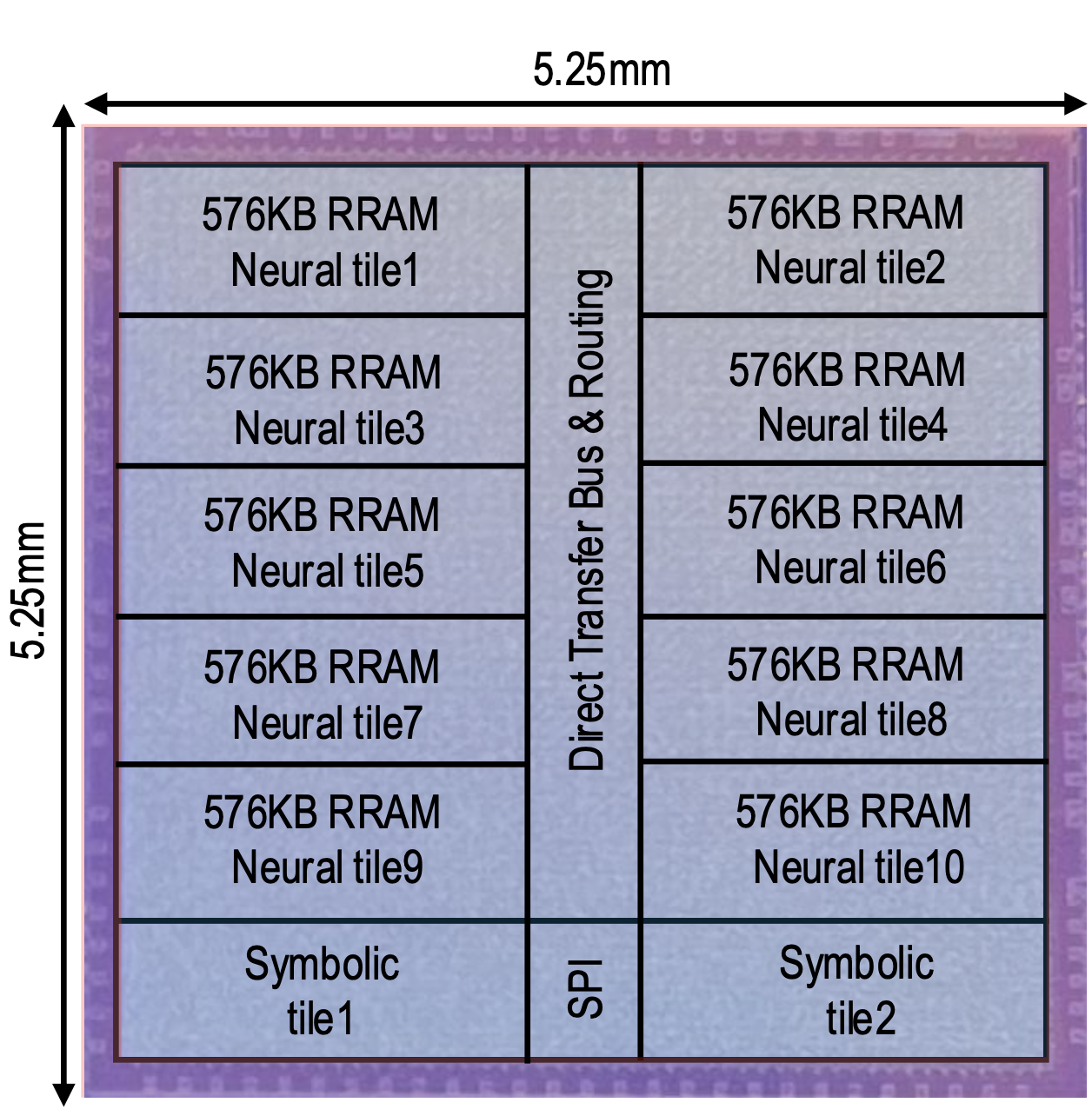

We take a vertically-integrated approach to enabling efficient and scalable neuro-symbolic computing, from workload benchmarking, hardware architecture, to FPGA prototyping and SoC tapeout [NeuS'25]. First, we conduct workload characterization to uncover key system behavior of neuro-symbolic [ISPASS'24] and compositional LLM-symbolic-probabilistic [ASPLOS'26] models. Second, we perform system optimization and build processing elements and dataflow architecture for neuro-symbolic computing [HPCA'25] and compositional LLM-symbolic-probabilistic computing [HPCA'26]. Third, we develop end-to-end framework with automated architecture generator for agile neuro-symbolic FPGA deployment [DAC'25]. Finally, we tape out a programmable heterogeneous SoC chip with integrated RRAM/SRAM datapath, scheduler-informed power management, and programming support for neuro-symbolic AI models [JSSC'26]. Through this synergistic cross-layer co-design, we demonstrate the feasibility of deploying efficient neuro-symbolic cognitive systems at scale.

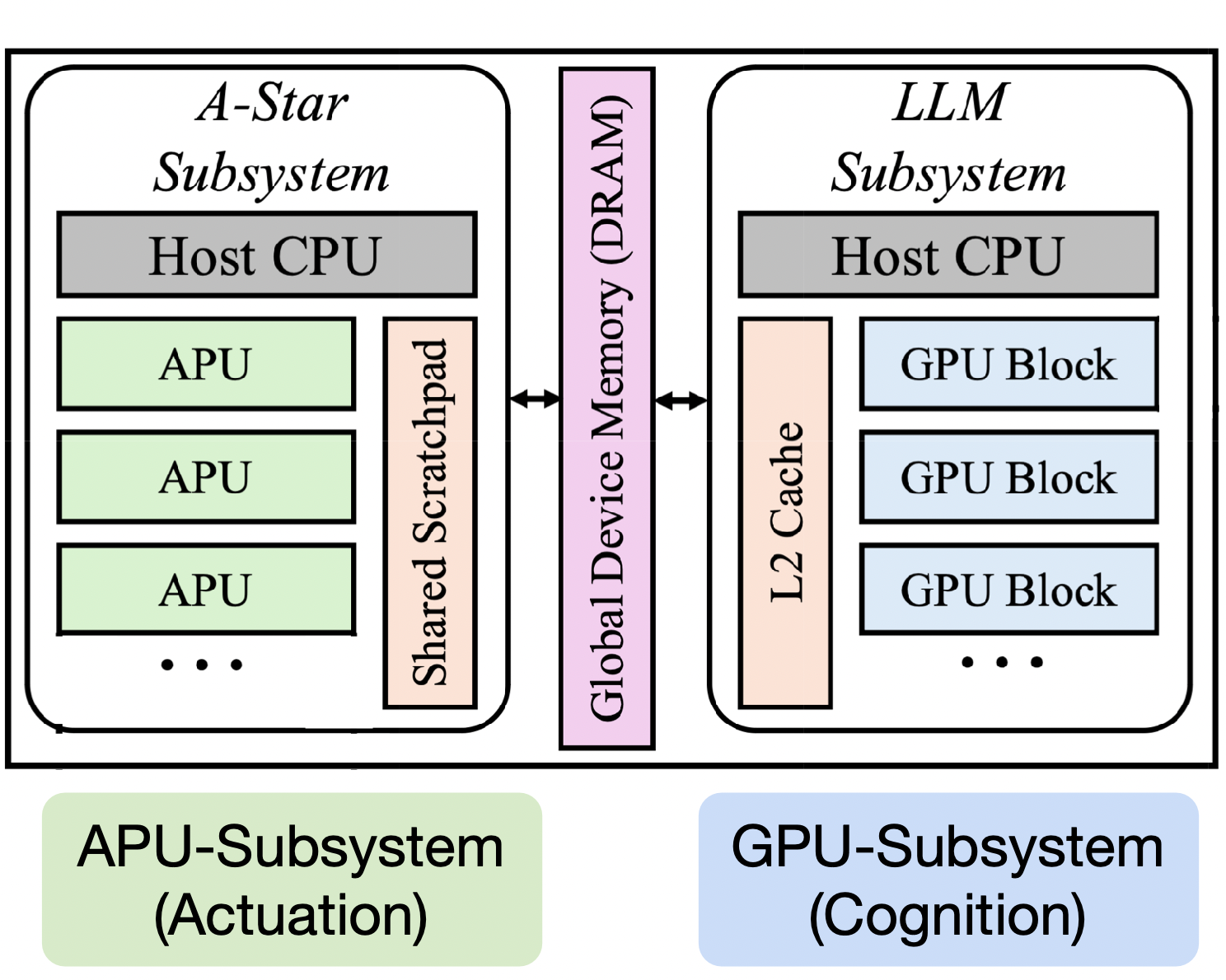

We also explore employing neuro-symbolic computing in embodied AI systems by integrating high-level planning-reasoning and low-level perception-control modules. Through system characterization [ISPASS'25] and development of dual memory system, hierarchical cooperation, and heterogeneous SoC architecture [ASPLOS'25], we aim to build more efficient and intelligent human-cognition-like physical AI systems that can better perceive, understand, reason, and interact with the complex real world.

Related Papers

|

Zishen Wan, Che-Kai Liu, Hanchen Yang, Ritik Raj, Arijit Raychowdhury, Tushar Krishna International Conference on Neuro-symbolic Systems (NeuS), 2025 Selected as Oral Presentation Paper This work presents our vertically integrated approach to enabling efficient and scalable neuro-symbolic computing—spanning workload benchmarking, hardware architecture, FPGA prototyping, and SoC tapeout. Through this cross-layer design, we demonstrate the feasibility of neuro-symbolic cognitive systems at scale. |

Workload Characterization

|

Zishen Wan, Che-Kai Liu, Hanchen Yang, Ritik Raj, Chaojian Li, Haoran You, Yonggan Fu, Cheng Wan, Ananda Samajdar, Yingyan (Celine) Lin, Tushar Krishna, Arijit Raychowdhury IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), 2024 Best Poster Award, DARPA SRC JUMP2.0 CoCoSys Center 2024 Paper / Slide / Media We systematically categorize neuro-symbolic AI workloads, conduct workload characterizations across hardware platforms, and identify cross-layer optimization opportunities for neuro-symbolic systems. |

System Optimization

|

Zishen Wan, Hanchen Yang, Ritik Raj, Joongun Park, Chenyu Wang, Arijit Raychowdhury, Tushar Krishna ACM Inter Conf on Architectural Support for Programming Languages and Operating Systems (ASPLOS), 2026 Best Paper Award, DARPA SRC JUMP 2.0, 2025 Paper Compositional AI integrates LLMs, symbolic, and probabilistic modules to enhance interpretability, robustness, and trustworthiness for cognitive applications. This paper presents a comprehensive system-level analysis of neuro-symbolic-probabilistic AI and reveals its key performance characteristics. |

Hardware Architecture

|

Zishen Wan, Che-Kai Liu, Jiayi Qian, Hanchen Yang, Arijit Raychowdhury, Tushar Krishna IEEE International Symposium on High-Performance Computer Architecture (HPCA), 2026 Paper (To appear) We propose REASON, an algorithm-system-architecture framework that accelerates the “slow-thinking” components of cognitive AI -- logical deduction, constraint solving, and probabilistic reasoning -- through common representation, reconfigurable architecture, and tight GPU integration for hybrid LLM + symbolic agentic workflows. |

|

Zishen Wan*, Hanchen Yang*, Ritik Raj*, Che-Kai Liu, Ananda Samajdar, Arijit Raychowdhury, Tushar Krishna International Symposium on High-Performance Computer Architecture (HPCA), 2025 Best Paper Award, DARPA SRC JUMP 2.0, 2024 Paper / Slide / Slide (long version) / Poster / Media We propose CogSys, a characterization and co-design framework dedicated to neurosymbolic AI system acceleration, aiming to win both reasoning efficiency and scalability. |

|

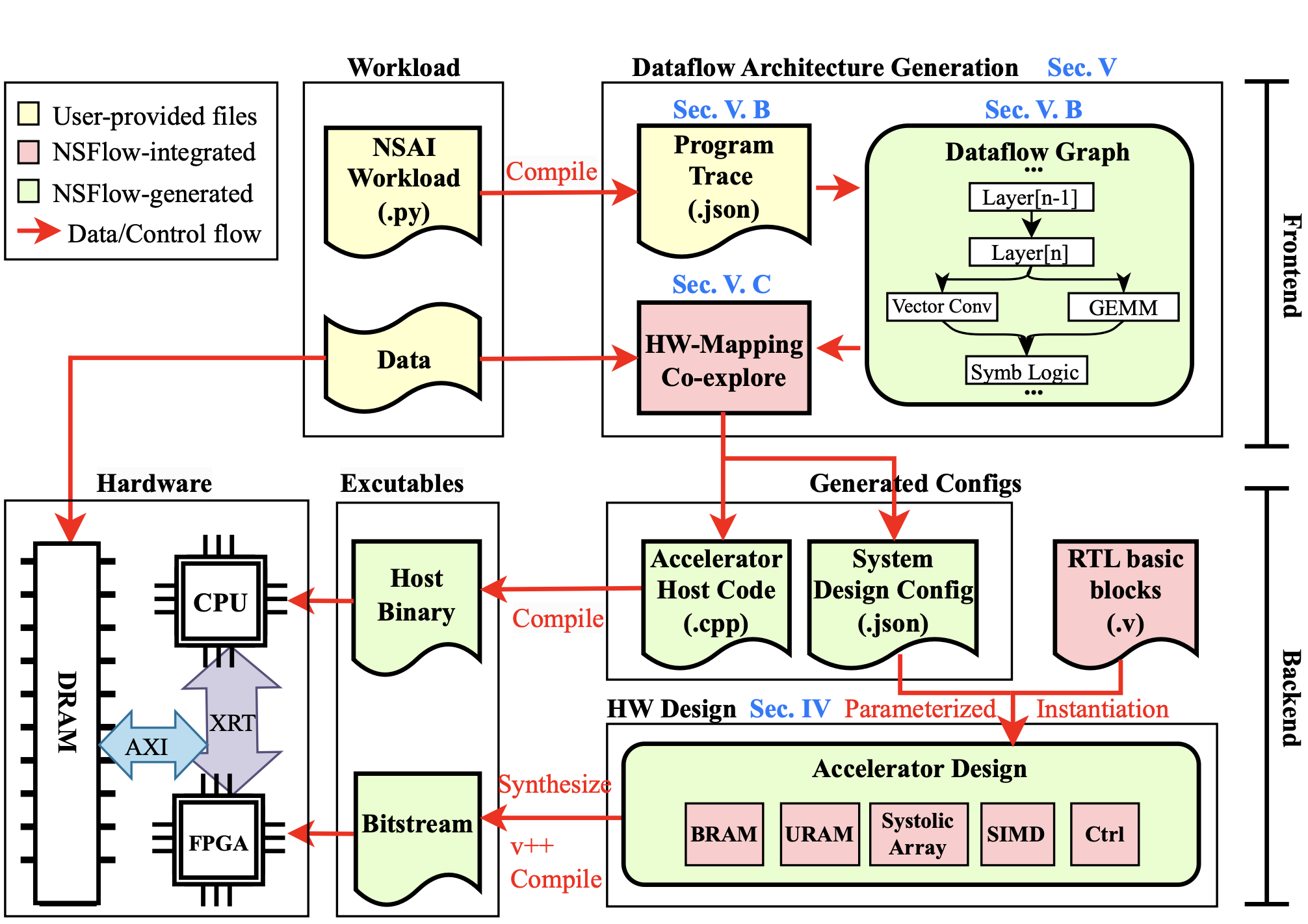

Hanchen Yang*, Zishen Wan*, Ritik Raj, Joongun Park, Ziwei Li, Ananda Samajdar, Arijit Raychowdhury, Tushar Krishna ACM/IEEE Design Automation Conference (DAC), 2025 Paper / Slide We propose NSFlow, an FPGA framework for efficient, scalable, and adaptive across neuro-symbolic systems. NSFlow features a design architecture generator that identifies workload data dependencies and creates dataflow architectures, as well as reconfigurable array with flexible compute units and re-organizable memory. |

|

Zishen Wan, Che-Kai Liu, Hanchen Yang, Ritik Raj, Chaojian Li, Haoran You, Yonggan Fu, Cheng Wan, Sixu Li, Youbin Kim, Ananda Samajdar, Yingyan (Celine) Lin, Mohamed Ibrahim, Jan M. Rabaey, Tushar Krishna, Arijit Raychowdhury IEEE Transactions on Circuits and Systems for Artificial Intelligence (TCASAI), 2024 Best Paper Award, DARPA SRC JUMP 2.0, 2024 Top-1 Most Cited Paper in all TCASAI Papers Paper / Fortune News / CoCoSys News We analyze the neuro-symbolic workload characteristics, and present a hardware acceleration case study for vector-symbolic architecture to improve the performance, efficiency, and scalability of neuro-symbolic computing. |

|

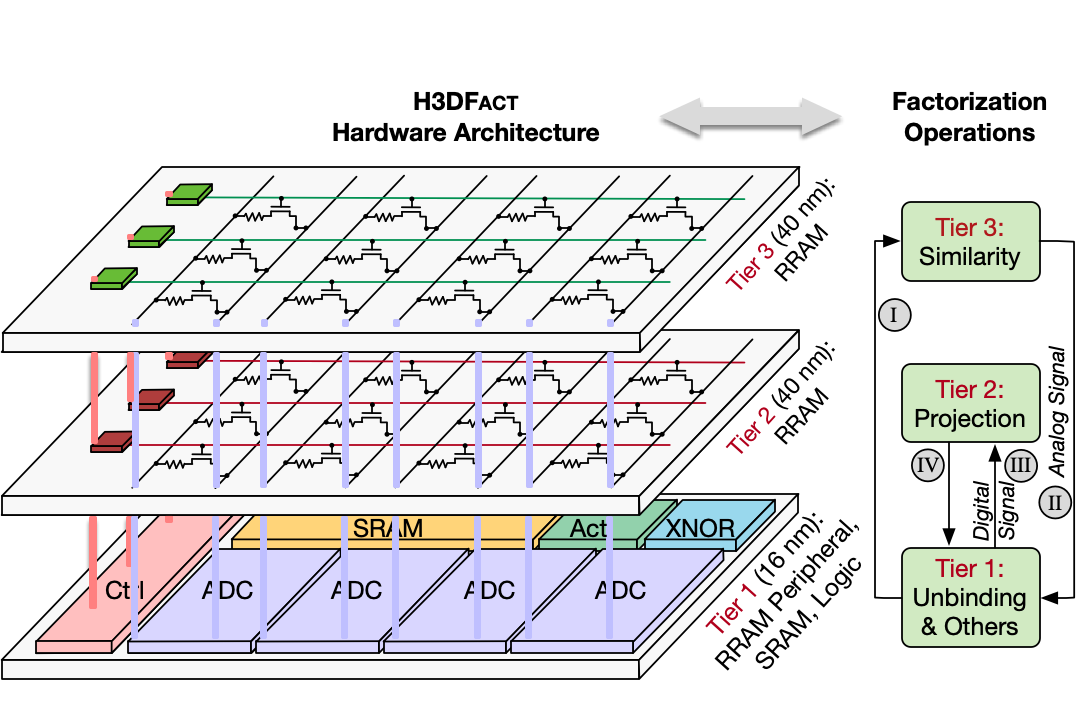

Zishen Wan*, Che-Kai Liu*, Mohamed Ibrahim, Hanchen Yang, Samuel Spetalnick, Tushar Krishna, Arijit Raychowdhury Design, Automation and Test in Europe Conference (DATE), 2024 Best Presentation Award, SRC TECHCON 2024 Paper / Slide / SRC News / GT News We present H3DFACT, the first heterogeneous 3D integrated in-memory compute engine capable of efficiently factorizing high-dimensional holographic representations towards next-generative cognitive AI. |

|

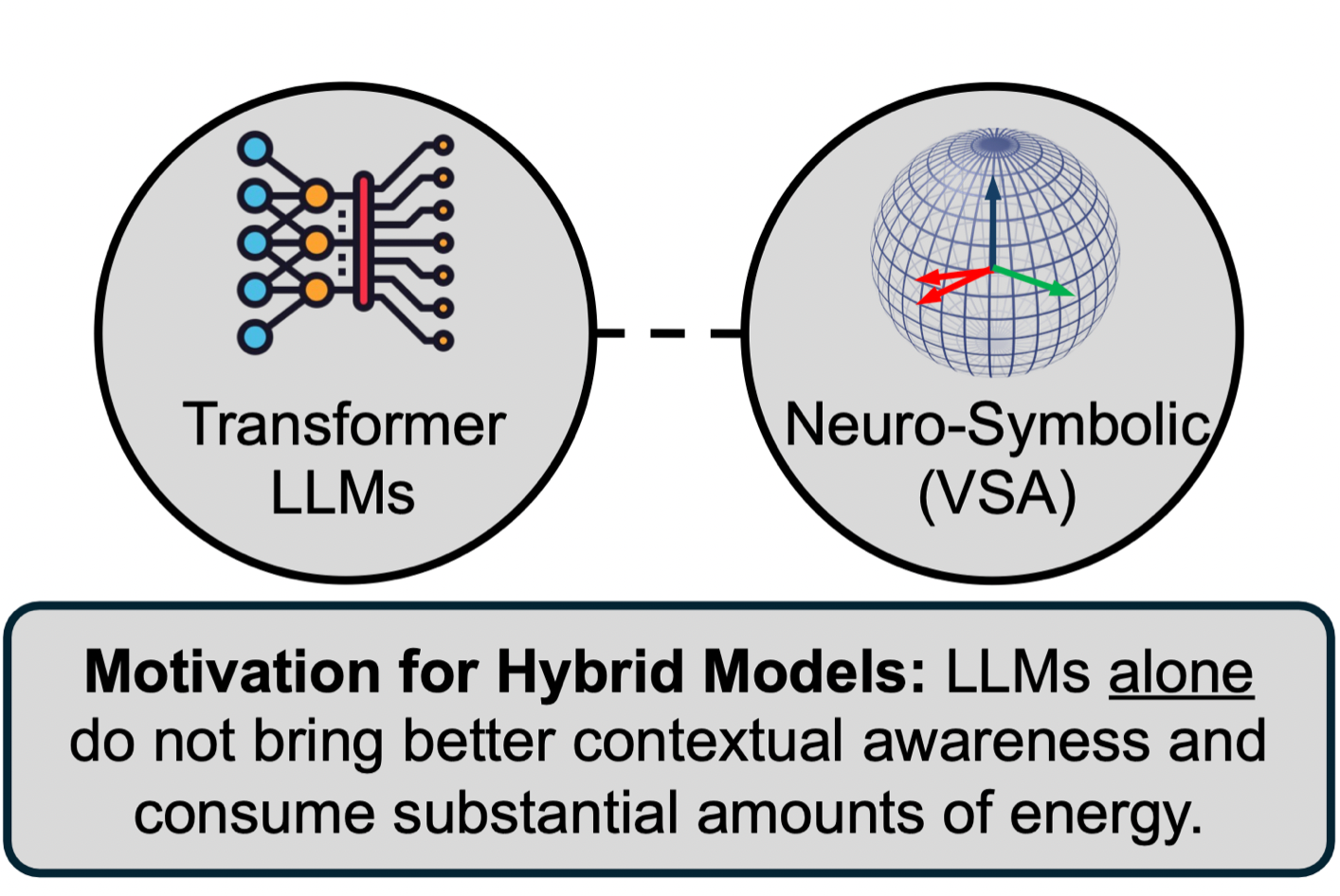

Mohamed Ibrahim, Zishen Wan, Haitong Li, Priyadarshini Panda, Tushar Krishna, Pentti Kanerva, Yiran Chen, Arijit Raychowdhury ACM/IEEE Embedded Systems Week (ESWEEK), 2024 Paper / Slide We analyze the computational challenges of integrating LLMs and neuro-symbolic architecture, and explore state-of-the-art solutions, focusing on the memory-centric computing principles at both algorithmic and hardware levels. |

Chip Tapeout

|

Che-Kai Liu*, Zishen Wan*, Young-Seok Noh, Mohamed Ibrahim, Samuel D. Spetalnick, Tushar Krishna, Win-San Khwa, Ashwin Sanjay Lele, Yu-Der Chih, Meng-Fan Chang, Arijit Raychowdhury IEEE Journal of Solid-State Circuits (JSSC), 2026 Paper (To appear) We tape out a fully programmable heterogeneous SoC that integrates RRAM/SRAM to efficiently accelerate a broad class of neuro-symbolic workloads. The chip features integrated RRAM and SRAM neural-symbolic data paths, ultra-dense RRAM macros, scheduler-informed power management, and flexible programming support, demonstrating end-to-end silicon system for generalizable and efficient neuro-symbolic AI inference. |

Embodied System Deployment

|

Zishen Wan, Yuhang Du, Mohamed Ibrahim, Jiayi Qian, Jason Jabbour, Yang (Katie) Zhao, Tushar Krishna, Arijit Raychowdhury, Vijay Janapa Reddi ACM Inter Conf on Architectural Support for Programming Languages and Operating Systems (ASPLOS), 2025 Selected as Industry-Academia Partnership (IAP) Highlight Best Paper Award, DARPA SRC JUMP 2.0, 2025 Paper / Slide / Slide (long version) / Poster / Media We propose ReCA, a characterization and system-architecture co-design framework dedicated to cooperative embodied AI agent system acceleration, aiming to enhance both long-horizon multi-objective planning task efficiency and system scalability. |

|

Zishen Wan, Jiayi Qian, Yuhang Du, Jason Jabbour, Yilun Du, Yang (Katie) Zhao, Arijit Raychowdhury, Tushar Krishna, Vijay Janapa Reddi IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), 2025 Paper / Slide This paper systematically categorizes the workload characteristics of embodied agent systems and presents a benchmark suite to evaluate their task performance and system efficiency, and suggests system optimization strategies to improve the performance, efficiency, and scalability of future embodied system design. |

Media Coverage

- Georgia Tech News: Wan Wins First Place at Premier Computing Ph.D. Forum (07/2025)

- Georgia Tech News: CoCoSys Develops Groundbreaking Neuro-Symbolic AI Chip (05/2025)

- Fortune News: Generative AI can’t shake its reliability problem, some say ‘neurosymbolic AI’ is the answer (12/2024)

- CoCoSys News: Research Scholar Spotlight from DARPA SRC JUMP2.0 Program (12/2024)

Acknowledgments

This work was supported in part by CoCoSys, one of seven centers in JUMP 2.0, a Semiconductor Research Corporation (SRC) program sponsored by DARPA.